verilog菜鸟教程|Verilog语言基础知识:实例(二)

发布时间:2023-09-05来源:芯学长

verilog语法对于学习IC设计来说比较重要,它也是目前应用最为广泛的硬件描述语言,可以用来进行各种层次的逻辑设计,也可以进行数字系统的逻辑综合,仿真验证和时序分析等。芯学长带你了解verilog语法。

点击上方蓝色按钮可以免费下载verilog语法全部资料

之前给大家更新了以下内容,今天继续更新内容

一.Verilog语法知识简介

二、verilog实例

二、数据选择器

这里我们设计一个四选一选择器,对应地址与数据选择关系如下

显然采用case语句很方便,假设输入数据位宽是8bit,verilog代码如下:

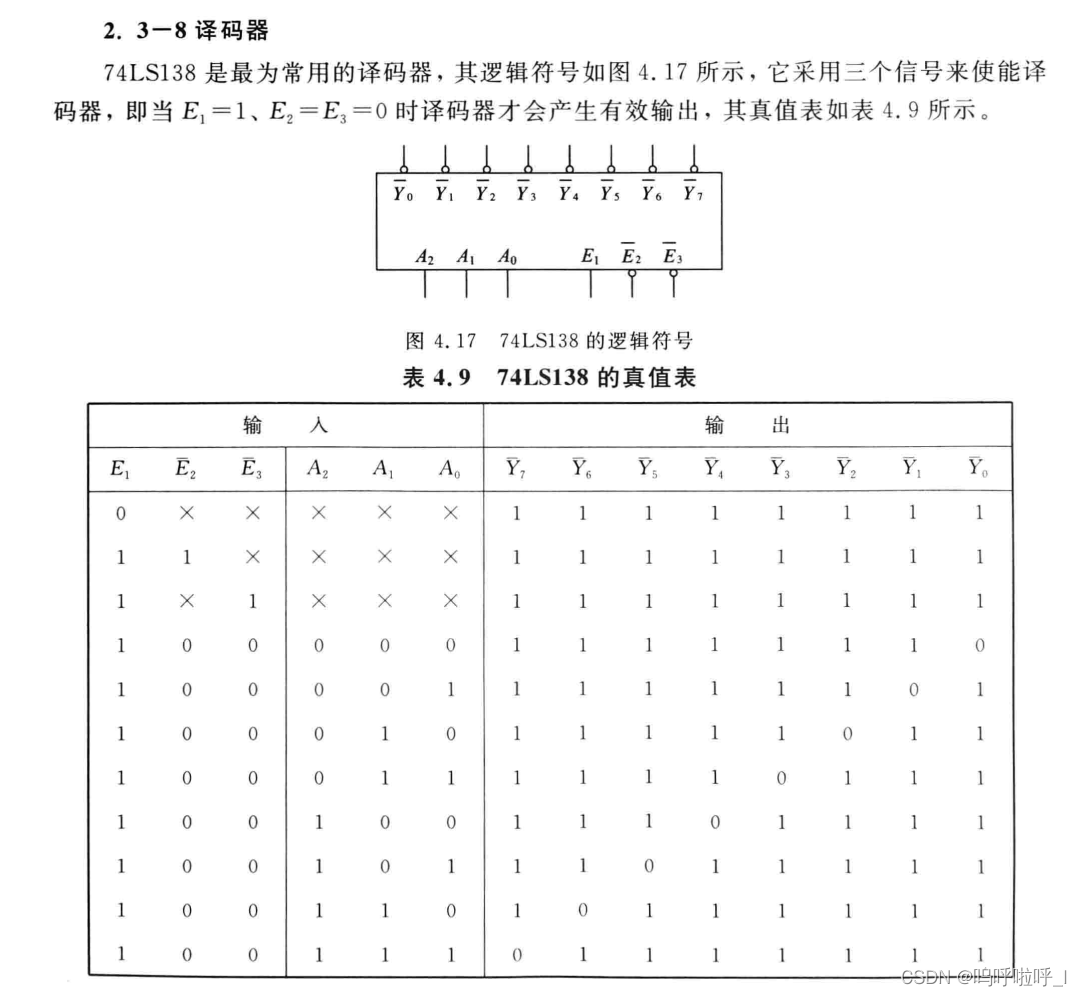

3.3-8译码器

对于3-8译码器,显然也是采用case语句很方便,观察真值表我们可以发现首先只有在E1、E2、E3均为1时才能工作,然后经过译码后的输出为0,其余输出为1,verilog代码如下:

4.加法器

对于一位加法器来说,有两个三个输入数据,分别是两个加数和一个低位对本位的进位,有两个输出,分别为本位和以及本位对高位的进位。

module add(A,B,Cin,S,Cout);

input A,B,Cin;

output S,Cout;

assign {S,Cout} = A+B+Cin;//S和cout拼接后,cout代表1bitS代表0bit,如果有进位那么会给Cout赋1

endmodule

那对于两位数的相加呢?其实我们可以把他拆为两个一位数相加,然后用上面的模块直接实现一位数相加。

那这里涉及到模块的例化(简单理解成函数的调用),下面给出例化的例子。

add为要例化的模块名,inst_add为例化给他指定的名字(自己随便定义,只要符合起名字的规则),

.Cout为使用模块的信号名,括号里的Cout为调用时传递给它的信号名,两个可以不一样。

两位数加法verilog

第一次调用模块的输出Cout作为第二次调用模块的输入Cin

点击上方蓝色按钮可以免费下载verilog语法全部资料

【免责声明】:本站部分文章为转载或网友发布,目的在于传递和分享信息,并不代表本网赞同其观点和对其真实性负责;文章版权归原作者及原出处所有,如涉及作品内容、版权和其它问题,我们将根据著作权人的要求,第一时间更正或删除。